SI/PI/EMC分(fēn)析

仿真介紹

SI 、PI、EMC、DFM 全面的仿真指導設計(jì)

仿真優化設計(jì)方案,設計(jì)更可(kě)靠,可(kě)行性更高

10多年(nián)的仿真工(gōng)程師(shī)确保仿真的正确性

可(kě)以實現10G以上高速信号的仿真分(fēn)析

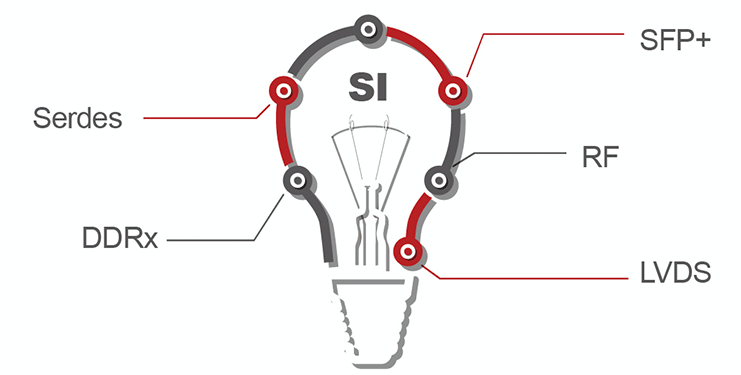

SI-Signal Integrity

信号完整性分(fēn)析

設計(jì)規則、拓撲結構前仿

反射、串擾、時序分(fēn)析

多闆聯合系統分(fēn)析

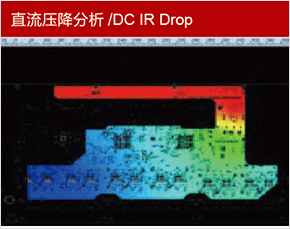

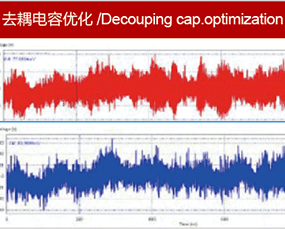

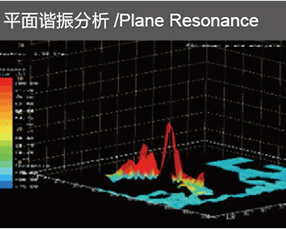

PI-Power Integrity

電源完整性分(fēn)析

直流壓降分(fēn)析

平面諧振分(fēn)析

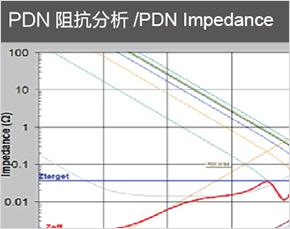

PDN阻抗分(fēn)析

去(qù)耦電容優化分(fēn)析

EMC

電磁兼容性分(fēn)析

EMC設計(jì)

EMC整改

EMC測試

DFM-Design for Manufacture

可(kě)生(shēng)産性設計(jì)分(fēn)析

DFF可(kě)制造性分(fēn)析

DFA可(kě)組裝性分(fēn)析

DFT可(kě)測試性分(fēn)析

信号仿真介紹

支持IBIS模型、Hspice模型和S參數模型

頻域、時域、通道多種仿真分(fēn)析手段、保證高速傳輸性能

綜合考慮反射、串擾、振鈴、眼圖、抖動、誤碼率、S參數

DDR3,DDR3L,DDR4,PCIE,Serdes,SFP+大(dà)量仿真案例,

擁有豐富實戰經驗

| 主要仿真分(fēn)析的項目 | |

|---|---|

| 延時計(jì)算 /Delay Caculate | 拓撲結構分(fēn)析 /Topology analysis |

| 反射仿真 /Reflection | 阻抗計(jì)算 /Impedance Cal |

| 串擾仿真 /Crosstalk | 疊層分(fēn)析 /Stack up |

| 時序分(fēn)析 /Static timing analysis | 同步切換噪音 /SSN simulation |

| S 參數提取 /S-parameter | 串并行接口仿真 /Serial Parallel link |

電源完整性仿真

設計(jì)可(kě)制造性

【可(kě)制造性設計(jì)就(jiù)是在設計(jì)階段考慮産品的可(kě)制造性和可(kě)裝配性等要素,使得(de)産品以最低成本、最短(duǎn)的時間、最高的質量制造出來(lái),

DFM是并行工(gōng)程的核心技術(shù),它的關鍵是設計(jì)信息的工(gōng)藝分(fēn)析、制造合理(lǐ)性評價和設計(jì)改進的建議(yì),通過模拟系統,實現仿真與設計(jì)過程同步,

模拟從(cóng)設計(jì)、制闆到組裝的整個生(shēng)産過程,使用DFM理(lǐ)念的設計(jì)方式可(kě)以減少試産次數,加快(kuài)研發周期,

設計(jì)前期把生(shēng)産裝配的問(wèn)題考慮到位,保證PCB設計(jì)一次性成功的關鍵。